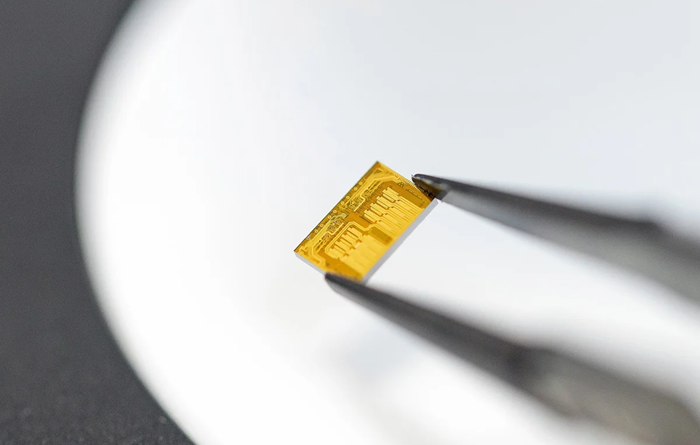

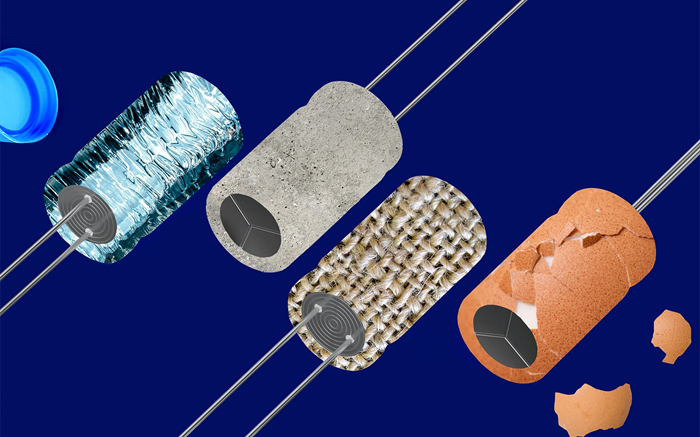

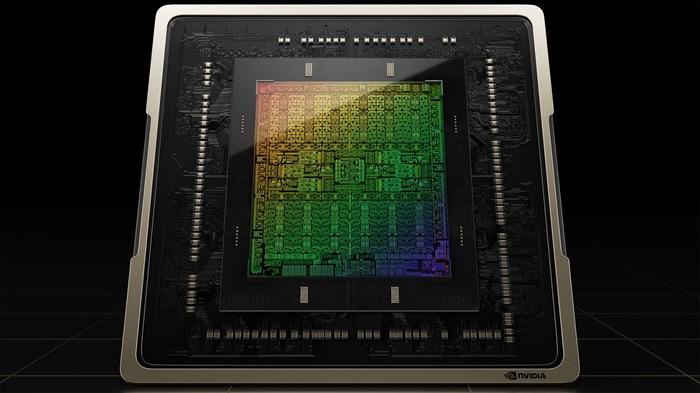

Nếu mở bên trong các bộ xử lý AI tiên tiến từ AMD hay Nvidia, có thể thấy một cấu trúc quen thuộc: GPU nằm ở trung tâm và được bao quanh bởi các chip bộ nhớ băng thông cao (HBM).

Những chip bộ nhớ này được đặt sát nhất có thể với bộ xử lý nhằm giảm độ trễ và năng lượng tiêu tốn khi truyền dữ liệu, một trong những nút thắt lớn nhất của tính toán AI. Tuy nhiên, các nhà nghiên cứu đặt ra một câu hỏi táo bạo hơn: điều gì sẽ xảy ra nếu thay vì đặt cạnh, bộ nhớ được xếp chồng trực tiếp lên trên GPU?

Viện nghiên cứu Imec đã thử nghiệm ý tưởng này bằng các mô phỏng nhiệt tiên tiến và phát hiện ra một thực tế đáng lo ngại. Khi chuyển từ kiến trúc 2.5D hiện tại sang xếp chồng 3D, nhiệt độ bên trong GPU có thể tăng gấp đôi, vượt xa ngưỡng hoạt động an toàn và khiến con chip không thể vận hành. Tuy nhiên, thay vì dừng lại, nhóm nghiên cứu tiếp tục tìm kiếm các giải pháp kỹ thuật để kiểm soát nhiệt độ và đưa thiết kế này trở nên khả thi.

Trong cấu trúc 2.5D đang được sử dụng phổ biến, GPU và các chip HBM cùng nằm trên một lớp trung gian gọi là bộ chuyển đổi trung gian, được kết nối bằng hàng nghìn liên kết đồng siêu nhỏ. Mô hình này cho phép GPU hoạt động ở mức nhiệt khoảng 70°C với công suất tiêu thụ hơn 400 watt, trong khi bộ nhớ tiêu thụ thêm khoảng 40 watt. Nhiệt lượng được tản ra chủ yếu từ phía trên nhờ hệ thống làm mát bằng chất lỏng, vốn đã trở thành tiêu chuẩn trong các trung tâm dữ liệu AI hiện đại.

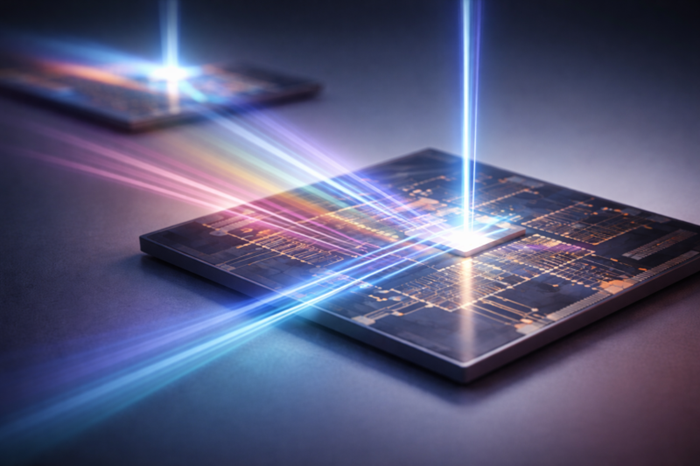

Tuy nhiên, cách bố trí này có những hạn chế rõ ràng về khả năng mở rộng, đặc biệt khi nó chiếm mất không gian hai bên GPU, làm giảm khả năng kết nối trực tiếp giữa các GPU trong tương lai. Ngược lại, kiến trúc 3D hứa hẹn mang lại băng thông cao hơn, độ trễ thấp hơn và tiết kiệm diện tích đóng gói. Nhưng phiên bản đơn giản nhất của việc xếp chồng, đặt HBM trực tiếp lên GPU, lại khiến nhiệt độ tăng vọt lên khoảng 140°C, vượt xa mức an toàn thông thường.

Để giải quyết vấn đề này, các nhà nghiên cứu đã tiến hành hàng loạt tối ưu hóa. Một trong những bước đầu tiên là loại bỏ một lớp silicon trung gian không còn cần thiết trong cấu trúc mới. Điều này liên quan đến cách HBM hoạt động: vốn dĩ HBM là một chồng nhiều lớp DRAM mỏng, kết nối theo chiều dọc và gắn với một “base die” để điều phối dữ liệu. Khi đặt trực tiếp lên GPU, vai trò trung gian này trở nên dư thừa vì dữ liệu có thể truyền thẳng vào bộ xử lý. Dù thay đổi này chỉ giúp giảm nhiệt độ vài độ, nó lại mở ra khả năng tăng mạnh băng thông giữa bộ nhớ và GPU.

Lợi thế băng thông này dẫn đến một chiến lược thú vị: giảm tốc độ hoạt động của GPU. Trong các mô hình AI lớn, hiệu năng thường bị giới hạn bởi tốc độ truy cập bộ nhớ hơn là sức mạnh tính toán thuần túy. Khi băng thông tăng lên nhờ kiến trúc 3D, GPU không cần chạy ở tốc độ tối đa mà vẫn đạt hiệu suất cao. Việc giảm xung nhịp giúp hạ nhiệt độ đáng kể, đồng thời vẫn đảm bảo hiệu năng tổng thể được cải thiện.

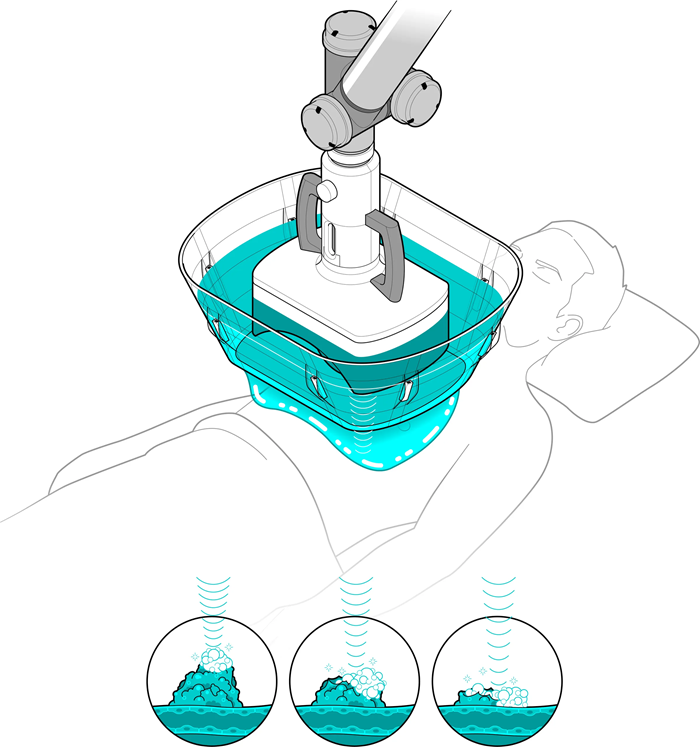

Bên cạnh đó, nhóm nghiên cứu cũng tối ưu lại chính cấu trúc HBM để tăng khả năng dẫn nhiệt. Họ giảm số lượng chồng bộ nhớ nhưng mở rộng kích thước, làm mỏng các lớp trên cùng và bổ sung thêm vật liệu dẫn nhiệt xung quanh. Những thay đổi này giúp giảm nhiệt độ xuống mức khoảng 88°C. Cuối cùng, bằng cách bổ sung hệ thống làm mát ở cả mặt dưới của chip, thay vì chỉ phía trên như trước, nhiệt độ tiếp tục giảm thêm, gần trở lại mức an toàn ban đầu.

Dù kết quả nghiên cứu cho thấy việc xếp chồng 3D là khả thi về mặt kỹ thuật nếu được tối ưu đúng cách, các nhà khoa học vẫn chưa khẳng định đây là hướng đi tối ưu nhất. Một phương án ngược lại, đặt GPU lên trên HBM, cũng đang được cân nhắc vì có thể giúp tiếp cận hệ thống làm mát tốt hơn, dù thiết kế sẽ phức tạp hơn nhiều khi năng lượng và dữ liệu phải đi xuyên qua các lớp bộ nhớ.

Những nghiên cứu này, được trình bày tại IEEE International Electron Device Meeting 2025, cho thấy tương lai của chip AI không chỉ nằm ở việc tăng sức mạnh xử lý, mà còn phụ thuộc vào cách con người giải quyết những giới hạn vật lý như nhiệt độ và không gian. Trong cuộc đua này, việc “xếp chồng” không chỉ là bài toán kỹ thuật, mà còn là thử thách về sự cân bằng giữa hiệu năng và khả năng tồn tại của chính con chip.